[ILS] 신뢰성(Reliability) 설계 Guideline

- ichkan1

- 2021년 9월 14일

- 21분 분량

목 차

1. 개요... 1

2. 부품 신뢰성 고려사항... 2

2.1 부품선택, 적용 및통제(Parts Selection, Application and Control). 2

2.1.1 부품 선택, 적용 및 통제(PSAC) 프로그램의 목표... 2

2.1.2 부품 선택, 적용 및 통제(PSAC) 개발 계획... 3

2.1.3 공급업체 및 장비 선정... 3

2.1.4 우선순위 부품목록(Preferred Parts List) 설정... 4

2.1.5 장치 규격서개발(Develop Device Specifications). 6

2.1.6 검사 절차결정(Determine Screening Procedures). 7

2.1.7 자료 수집및 분석(Data Collection and Analysis). 9

2.2 특수 부품 고려사항(Special Part Considerations). 10

2.3 부품 부하 경감(Part Stress Derating). 11

3. 조립체 신뢰성 고려사항... 14

3.1 열 관리(Thermal Management). 14

3.2 상호 접속기술(Interconnection Techniques). 16

3.2.1 외부 컨넥터(External Connectors). 16

3.2.2 전선 컨넥터(Wire Connections). 17

3.2.3 표면 실장연결(Surface Mount Connections). 17

3.2.4 내부 연결(Internal Connections). 18

3.2.5 본딩 연결(Bonding Connection). 18

3.2.6 본딩 연결에 대한 설계 Guidelines. 19

3.3 조립체 수준의검사 범위(Testability Criteria_Assembly Level). 20

4. 장비/시스템 신뢰성 고려사항.. 23

4.1 시스템 고장 허용 범위... 23

4.2 환경 특성(Environmental Characterization). 26

4.2.1 수동 환경기록(Passive Environmental Records). 27

4.3 치명적인 품목신뢰성(Critical Item Reliability). 28

4.3.1 치명적인 품목은 무엇인가... 28

4.3.2 어떻게 치명적인 품목을 식별하는가.. 28

4.3.3 무엇이 치명적인 품목을 발생시키는가.. 28

4.3.4 치명적인 품목제어(Critical Item Control). 28

4.4 소프트웨어 신뢰성(Software Reliability). 30

4.4.1 소프트웨어 개발모델(Software Development Models). 30

4.4.2 소프트웨어 개발Guidelines(Software Development Guidelines). 32

4.4.3 소프트웨어 개발접근(Software Development Approaches). 33

4.4.4 소프트웨어 재사용(Software Reuse). 34

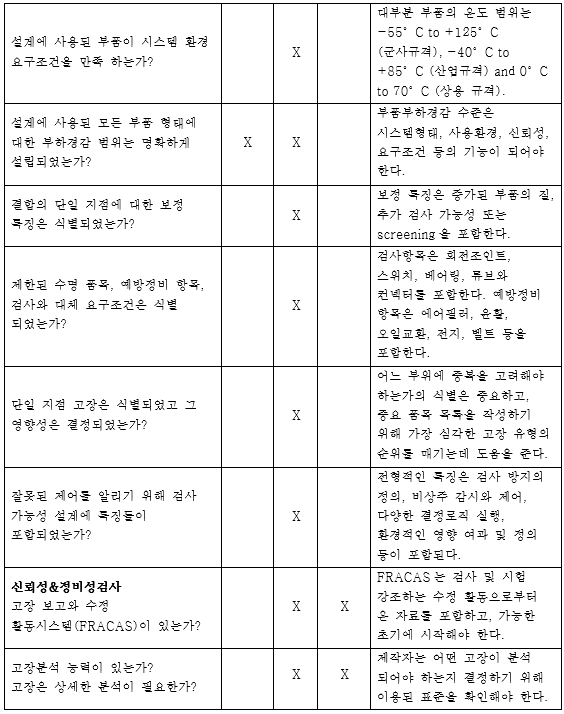

4.5 시스템 수준의검사 범위(Testability Criteria_System Level). 35

4.5.1 최상위 수준 설계 고려사항.. 35

4.5.2 시스템 Built-In Test (BIT). 35

4.6 시스템 전자기Guidelines. 36

4.7 기계 시스템(Mechanical Systems). 38

4.8 생산품 검토 질문 유형... 42

5. 약어... 47

표목차

표 1 부품 공급업체에 대한 대표적인 질문... 5

표 2 PPL 없는 설계의 부정적인 영향... 6

표 3 선별 검사의 예... 8

표 4 Screening/Test 요구조건 vs 성숙도... 8

표 5 Screen/Test Sources의 연관된 장점... 9

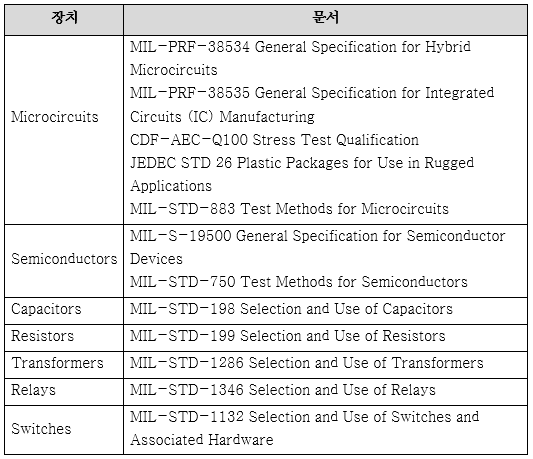

표 6 상용 및 군사 부품 검사 문서... 9

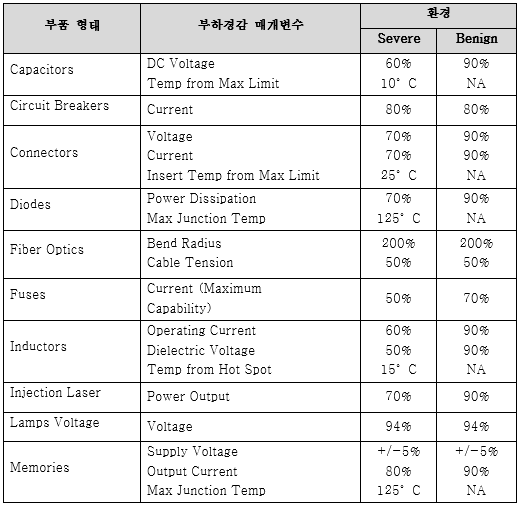

표 7 부품 부하경감 수준... 11

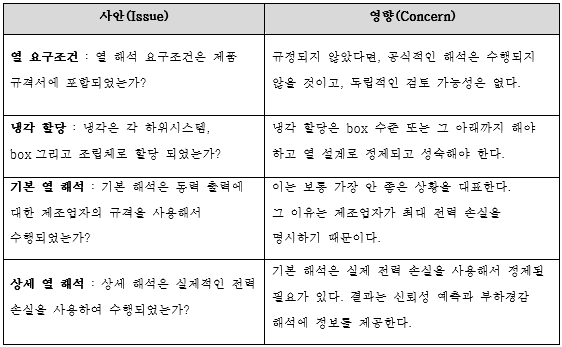

표 8 열 설계 사안... 14

표 9 냉각 기술 제한... 15

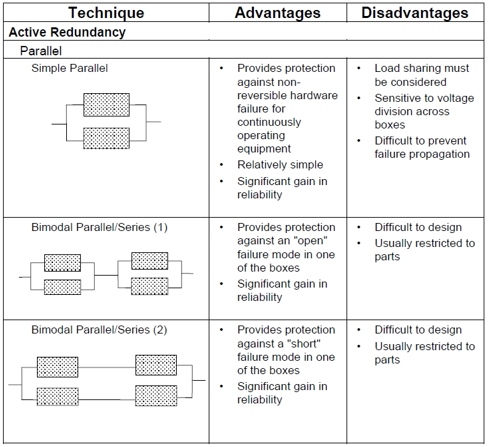

표 10 고장 허용 범위 기술 요약... 23

표 11 중요 품목 통제 점검표... 29

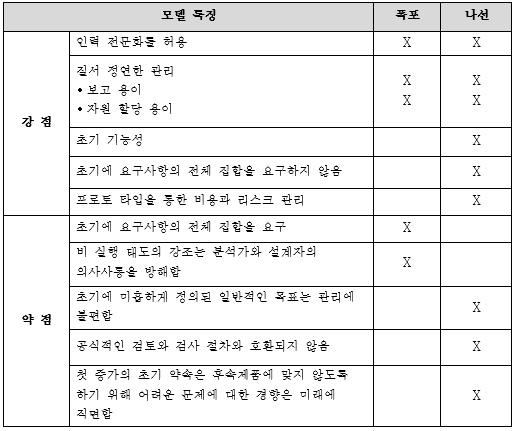

표 12 두 모델의 강점과 약점... 32

표 13 전자 시스템의 전자기 성능 향상을 위한 설계 지침... 38

표 14 기계적인 고장의 주요 매커니즘... 39

표 15 기계적 설계의 환경적인 영향... 40

표 16 주요 제품 검토... 43

표 17 생산품 검토 점검표... 44

그림목차

그림 1 부품 선택, 적용 및 통제 Process Flow.. 2

그림 2 공급업체 선정 방법론... 4

그림 3 고장율 vs. 시간 및 성숙도... 7

그림 4 외부 컨넥터 삽입 예... 16

그림 5 전선 연결의 예... 17

그림 6 표면 실장 연결의 예... 17

그림 7 내부 연결의 예... 18

그림 8 본딩 연결의 예... 18

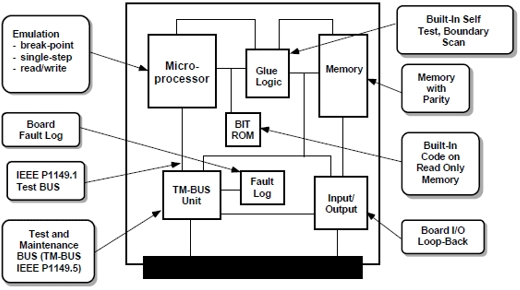

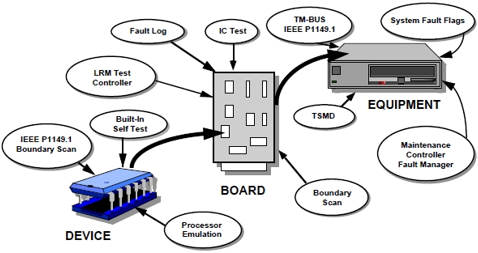

그림 9 모듈 검사 원천... 22

그림 10 TSMD 블록 다이어그램.. 26

그림 11 품질 소프트웨어 개발을 위한 폭포 모델... 31

그림 12 나선 모델... 31

그림 13 계층적인 검사... 36

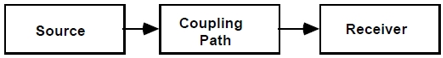

그림 14 전자기 설계의 기초... 37

그림 15 전자기 설계 옵션 vs 수행 비용... 37

그림 16 항공 시스템의 환경과 연관된 고장 분포... 40

1. 개요

본 문서는 ooo 체계개발 시 고려해야 할 신뢰성 설계에 대한 지침을 제공하며, 설계자는 본 문서의 신뢰성 관련 요소들을 반드시 고려하여 설계를 해야 한다.

가. 고객(소요군)의 신뢰성 요구는 무기체계의 운영 준비 상태(Readiness), 운영 수명, 운영 지원성, 극단 환경에서 만족할 만한 성능 측면을 최우선 사항으로 고려 함

나. 따라서 신뢰성 설계는 무기체계 설계에 있어 매우 중요한 고려사항 이며, 설계자는 다음의 신뢰성 관련 요소들을 반드시 고려하여 설계 해야 함

다. 신뢰성 설계 고려요소

• 부품 신뢰성(Part Reliability)

• 조립체 신뢰성(Assembly Reliability)

• 장비/시스템 신뢰성(Equipment/System Reliability)

2. 부품 신뢰성 고려사항

2.1 부품 선택, 적용 및 통제(Parts Selection, Application and Control)

2.1.1 부품 선택, 적용 및 통제(PSAC) 프로그램의 목표

가. 제조 환경에 견딜 수 있고 사용 환경에서 제품의 설계 수명에 필요한 기능을

확실히 수행할 수 있는 부품과 재료의 선택

나. 부품과 재료를 선택하는데 있어서 효율적인 비용 고려

그림 1은 부품 선택, 적용 그리고 통제(PSAC) 과정의 흐름을 설명하고, 다양한 프로그램 업무들이 완성되는 것을 보여준다. 이러한 각각의 업무들은 각 시스템의 특정한 요구에 만족할 수 있도록 맞추어져야 한다.

그림 1 부품 선택, 적용 및 통제 Process Flow

추가적인 정보는 “MIL-STD-965”에 제공되어 있다.

2.1.2 부품 선택, 적용 및 통제(PSAC) 개발 계획

PSAC 과정에 포함된 이해, 정의 그리고 수행의 모든 업무는 PSAC 과정의 성공에 대한 열쇠이며, PSAC 계획안에 전체적으로 설명돼야 한다. 다음의 기능적인 분야의 대표 그리고 적극적인 참여는 공학적인 열정과 동시에 효과적인 PSAC 과정을 가능하게 하기 위해서 필수적 이다.

가. 부품 공학

나. 설계 공학

다. 신뢰성 공학

라. 제조 공학

마. 사용자

성곡적인 PSAC의 수행은 반드시 관리 참가와 분야 중 협력을 지키고 비용, 계획 및 성과에 대한 궁극적인 영향을 둔 어떤 다른 점 이라도 해결하는 지원이 있어야 한다. 신뢰성 분석 센터의 발행물 “부품 선정, 적용, 통제”는 이 계획의 발전에 일반적인 안내를 제공한다.

2.1.3 공급업체 및 장비 선정

PSAC 과정을 실행하는데 중요한 요소들은 판매회사의 평가, 선정 및 관리 그리고 부품의 선정이다. 통합된 정부에 의해서 결정된 기준은 출발점으로 이용될 수 있다. “MIL-BUL-103”은 표준 군 도면 활동의 목록을 제공한다. 반드시 엔지니어가 신뢰성 있는 공급업체로부터 부품을 선정하고 이용해야 한다. 그림 2는 잠재적인 공급업체를 평가 하는 방법을 보여준다. 판매업자 평가는 설계, 제조, 품질 및 신뢰도 정도를 분석해서 달성할 수 있다. 검사/입증은 문서화되고 기준이 된 시스템이 존재하고 사용되고 있는지 평가 할 것이다. 표 1에 있는 것과 같은 대표적인 질문들은 검사/입증 과정의 한 부분으로 사용될 것이다.

효과적인 부품 조건과 평가 방법론은 파괴적이고 물질적인 분석, 수명 분석, 탐지된 수준의 지속적인 감시 그리고 자료 분석이다. 분석 도구의 완전한 설명은 RAC 발행물 "Parts Selection, Application and Control"에 포함되어 있다.

그림 2 공급업체 선정 방법론

2.1.4 우선순위 부품 목록(Preferred Parts List) 설정

시스템 요구조건을 만족하기 위한 중요한 단계는 사용을 위해 추천된 부품들의 형태가 식별되는 우선순위 부품 목록의 준비이다. PPL의 설립을 위한 형식의 예는 MIL-STD-965에 나타나 있다. 부품 선정 및 통제 프로그램은 제품에 들어가는 새로운 부품의 수를 최소화하는 규격화의 수준을 위해 노력해야 하고, 여전히 효과적으로 신기술에 의해 제안된 이점을 이용하기 위하여 충분히 이용 가능하다. PPL이 없는 상품 설계의 결과는 표 2에 표시되어 있다.

표 1 부품 공급업체에 대한 대표적인 질문

• 품질 프로그램은 정의되고 수행되는가?

• 잠재적인 고장 매커니즘은 식별되었는가?

• 어떠한 교정 활동들이 할당 되었는가?

• 제작 자료와 공정은 문서화 되었는가?

• 공정 제어 준비가 되어 있는가?

• 부품이 지속적으로 생산되는가? 또는 간헐적으로 생산되는가?

• 어떠한 결한 수준이 나타나는가?

• 지속적인 향상을 위한 목표가 있는가?

• 고장 매커니즘의 수명주기는 제품의 예상 사용수명을 초과 했는가?

• 부품 고장의 원인을 식별하고 원인의 발생을 완화하기위해 제조

공정을 개선하기 위한 노력은 이루어지는가?

• 부품 검사 공정은 효율적인가?

• 높은 품질과 신뢰성의 결과로 사용되고 준수되는 설계 규칙이 있는가?

• 설계 변경은 분석 및 수량화 가능한 신뢰성과 품질에 미치는 영향

이후에 수행되는가?

• 중요 변경사항은 고객에게 통보되는가?

• 공급자는 정시 납품을 추적하고 입증하는가?

표 2 PPL 없는 설계의 부정적인 영향

• 단종되거나 단일 공급원의 부품과 재료의 선정

• 공급원 축소의 가능성

• 입증되지 않거나 또는 실험적인 기술의 사용

• 제조 공장과의 불일치

• 재고품의 증가와 비용 상승

• 추가된 많은 공급업자 때문에 공급업체의 품질 모니터링이 힘듬

• "ship-to-stock" 또는 "just-in-time" 구매 기회의 손실

• 대량 구매의 이익 제한

• 증가된 비용 및 일정 지연

• 추가된 푸붐 특성의 차이에 대한 처리를 위해 부가적인 툴링과 조립 방법이 요구 됨

• 새로운 부품의 경험 부족과 불확실성으로 인해 신뢰성이 감소할 수 있음

• 추가된 부품 형태의 변동성 때문에 자동화 노력이 지연될 수 있음

2.1.5 장치 규격서 개발(Develop Device Specifications)

전기적인, 기계적인 부분 그리고 물리적인 특성들은 설계, 시험 및 획득을 위해 사용되는 장치 규격에 정의되어야 한다. 모든 작동 상태를 위해 적용 가능한 장치의 전기적인 성능 파라메터들은 신뢰성 파라메터를 포함하여 제품 성능 목표를 달성하는 것을 확신하기 위해 필수적으로 명시되어야 한다. 부품 규격은 운영 환경, 최악의 스트레스 수준, 수명기간 그리고 신뢰성 요구조건을 포함한 몇몇 요소들에 근거해야 한다. 적용할 수 있는 부품을 위한 회사 규격을 준비하기 위해 사용될 수 있는 예는 표준 군사 도면(Standard Military Drawing, SMD)이다. 이 형식은 산업계에 의해 검토되고, 조정되고 받아들여졌으며, 실제 적으로 명확하게 명시된 요구조건을 제공하는 규격의 개발에 사용될 수 있다. 세부사항은 MIL-HDBK-780의 표준화된 군사 도면 "Standardized Military Drawings."에서 제공된다. 게다가, “Analog Testing Handbook" 참고 2는 아날로그 장치의 규격에 대한 세부적인 정보를 제공한다.

2.1.6 검사 절차 결정(Determine Screening Procedures)

부품의 검사는 부품에 적용된 연속적인 스트레스로 구성된다. 검사의 목적은 잔여 부품의 수명 감소 없이 약해진 부품들을 제거하는 것 이다. 제작 공정이 결함이 없지 않기 때문에, 생산은 완벽하지 않고 제조 검사 과정에서 결함이 없는 부품을 보증하지 않는다. 성숙한 부품은 그림 3에 나타난 것과 같이 덜 성숙한 부품보다 더 신뢰할 수 있다.

그림 3 고장율 vs. 시간 및 성숙도 선별 검사는 그들의 목적이 다르기 때문에 반드시 수명 또는 신뢰성 검사와 구별되어야 한다. 검사는 모집단에 있는 부품들의 식별이나 삭제를 의도하지만 고장에 대한 높은 경향을 갖는다. 이것은 검사의 목적이기 때문에, 이것을 100% 기초로 행해져야 한다. 샘플을 기초로 수행된 수명 또는 신뢰도 검사의 목적은 특정한 작동 조건하에서 부품의 예상된 신뢰성을 정량화하기 위한 것이다. 효과적인 검사를 설계하기 위해서 잠재적인 고장 매커니즘, 관련된 발생 확율, 쉬운 탐지, 고장 시간, 고장 매커니즘이 많은 관련이 있는지 없는지를 이해하는 것이 필요하다. 만일 고장 매커니즘이 많이 연관되었다면 샘플링 검사로 충분할 수 있지만 진실로 무작위의 결함이 많은 관련이 없다면 스트레스 검사가 필요할 수 있다. 어떤 경우에도, 고장 매커니즘의 지식은 결정적이다. 전형적인 선별 검사 그리고 그와 관련된 효과는 표 3에 나타나 있다. 표 3 선별 검사의 예 • Temperature☆☆ • Temperature Cycling☆☆☆☆ • Thermal Shock☆☆☆☆ • Humidity☆☆ • Shock/Vibration☆☆ • Visual Inspection☆ • Electrical Test☆☆☆☆ • Power Cycling☆☆ 검사 효과는 검사된 부분 성숙의 강한 기능이다. 그림 3에 전형적인 고장율, 시간 함수 그리고 부분 성숙도 사이의 관계를 보여준다. 하지만, 과정의 성숙도는 오직 실험적인 증거로부터 결정될 수 있다. 그 과정은 높은 수익을 제공하고 매우 낮은 결함을 포함할 확률을 갖는 부품 생산의 능력이다. 표 4에 이 개념이 나타나 있다. 중요 강조사항은 품질에 위치해야 한다. 첫 번째 업무는 제작 라인에 기초한 공정 관리를 달성하는 것이다. 한 접근법은 in-line 검사와 감소된 end-of-line 검사를 같이 사용하는 것이다. 이것은 표본 검사 구조, 웨이퍼 그리고 전형적인 초소형 전기 장치를 위한 제품 검사를 포함한다. 이러한 절차는 in-line vs. end-of-life 시험 간에 상충점에서 평가 되어야만 한다.

표 4 Screening/Test 요구조건 vs 성숙도

Original equipment manufacturers(OEMs)는 어떤 조직이 스크린/검사를 수행할 것인가를 결정할 때 몇몇 선택권을 갖는다. 이러한 옵션들은 부품 제조업자, 부품 사용자(OEM) 및 독립적인 실험실을 포함한다. 이러한 결정을 할 때 몇몇 요소들은 고려되어야 한다. 이 요소들은 표 5에 각각의 잠재적인 스크린/검사 시설을 위한 요소의 질적인 순위를 따라서 요약되어 있다. 이것은 아주 주관적인 표이고 조건의 특정한 세트에 따라서 등급에 있는 큰 변이가 있을 것이라는 것을 주목해야 한다. 예를 들어 부분 제조업자 자료의 정확성은 수율(yield)에 민감한 자료 획득의 어려움 때문에 낮게 나타난다.

표 5 Screen/Test Sources의 연관된 장점

미 국방부, 전자 산업 협회, 국제 반도체 표준 협의기구, 자동차 산업 그리고 다른 산업 위원회는 초소형 회로 스크린을 설명하는 기존의 많은 문서들에 기여 했다. 크라이슬러, 델코와 포드로 구성된 자동차 전자 협의기구는 미소 전자 부품에 스크린 절차를 자동차 규격과 접목시키기 시작했다. 표 6은 부품 검사 안내에 대한 상업용, 군용 문서들의 목록이다. 2.1.7 자료 수집 및 분석(Data Collection and Analysis) PSAC 과정 흐름의 맥락에서 판매 업체, 장치 선정으로부터 나온 자료, PPL 및 장치 규격 개발 그리고 스크린 테스트 정의 과정은 PSAC 계획의 유효성을 결정하기 위해서 분석되어야 한다. 적합 하다고 식별되었을 때, 유효성을 향상시키기 위해 계획에 수정되어야 한다.

표 6 상용 및 군사 부품 검사 문서

참고 문헌: 1. Farrell, J. and N. Fuqua, "Parts Selection, Application and Control" (PSAC), Reliability Analysis Center, 1993. 2. "Analog testing Handbook" (ATH), Rome Laboratory/Reliability Analysis Center, 1993. 3. MIL-STD-883, "Test Methods and Procedures for Microelectronics," 1983. 4. MIL-H-38534, "General Specification for Hybrid (Microcircuits)," 1992. 5. MIL-PRF-38535, "General Specification for Integrated Circuits (Microcircuits) Manufacturing," 1995. 6. Automotive Electronics Council (Chrysler, Delco, Ford) CDF-AEL-Q-1000, "Stress Test Qualification for Automotive Grade Integrated Circuits," (9 June 1994). 7. JEDEC Standard 26, "Plastic Packages for Use in Rugged Environments," (Being prepared by EIA-JEDEC JC 13 committee.) 8. MIL-STD-965, "Parts Control Program," 1985. 2.2 특수 부품 고려사항(Special Part Considerations) 몇몇 부품은 잠재적인 신뢰성, 안전 또는 가용성 문제 때문에 각별한 주의를 요한다. 전통적으로, 빈번히 사용되는 부품 형태들은 초기에 부품 선택, 적용 그리고 통제 프로그램에 등록된다. 그러나 예상된 제품 신뢰성을 얻기 위해 성능 그리고 적시 배송, 초기 주의는 다음의 특성과 함께 반드시 고려되어야 한다. 가. 성능 제한 : 엄격한 환경 조건 또는 견고하지 않은 설계 활동 나. 신뢰성 제한 : 부품의 수명 제한 또는 비현실적으로 감소한 요구조건의 사용 다. 판매업자 : 과거의 배송, 가격, 성능 또는 신뢰성 문제의 기록 라. 구 기술 : 신뢰성 문제 마. 신기술 : 미성숙한 제조 기술을 사용한 부품 제작 또는 제한된 부품 사용 자료 1~3번째 범주는 예전 자료를 요구한다. 그리고 발생 또는 제공되는 대체 해결책을 최소화하기 위해서 행동을 정의한다. 4~5번째 범주는 기술 성숙도, 가용성 그리고 단종을 추적하기 위한 다른 획득 절차를 포함할 수 있는 성숙도와 신기술의 주제를 포함한다. 이러한 특성들을 정의하고 추적하는 것은 인식하고 있는 인원에 연관된 위험성을 경고할 것이다. 예를 들어, 플라스틱으로 포장된 장치가 사용된다면 그것의 기대 수명은 사용 환경의 기능으로 결정 되어야 한다. 그리고 나서 이 부품들을 운용하는 제품의 설계수명과 비교되어야 한다. 참고 문헌: 1. RADC-TR-88-124, "Impact of Fiber Optics on System Reliability/Maintain ability," Rome Laboratory, 1988. 2. MIL-PRF-38535, "General Specification for Integrated Circuits," 1995. 3. MIL-PRF-38534, "General Specification for Hybrid Microcircuits," 1995.

2.3 부품 부하 경감(Part Stress Derating)

부품에서 전기, 열 그리고 기계적인 부하의 특정한 등급 아래 수준까지 제한하는 행위를 부하경감이라고 한다. 만일 제품이 예상대로 신뢰성 있게 작동한다면, 한 가지 기여 요소는 실제적인 부품의 부하 경감을 위해 보수적인 설계 접근을 해야 한다. 표 7은 부품 형태에 대한 추천된 부하경감 요소를 나타낸다. 제공된 모든 비율은 별도로 분리되지 않았어도, 정격 값에 대한 감세 매개 변수이다. 온도 부하 경감은 분류된 것이 없다면 최대 비율이다. 해당 없음(NA) 용어는 최대 수준이 무해한 조건에 도달할 수 없는 상황을 나타낸다. 두 가지 수준 또는 안전 여유가 표시된다. 무해한 수준은 사무실 환경 과 같은 온화한 조건에서 제품이 작동하는 것이다. 심각한 수준은 자동차 또는 항공기 환경과 같은 거치 상태에서 제품이 작동하는 것이다.

표 7 부품 부하경감 수준

참고 문헌: 1. MIL-STD-975K, Notice 2, "NASA Standard Parts Derating," 1993. 2. RL-TR-92-11, "Advanced Technology Component Derating," Rome Laboratory, 1992. 3. TE000-AB-GTP-010, "Parts Derating Requirements and Application Manual," Naval Sea System Command, 1991. 4. ESD-TR-85-148, "Derating Application of Parts," Electronic System Center, 1985. 5. RADC-TR-84-254, "Reliability Derating Procedures," Rome Laboratory, 1984. 6. RADC-TR-82-177, "Reliability Part Derating Guidelines," Rome Laboratory, 1982.

3. 조립체 신뢰성 고려사항 3.1 열 관리(Thermal Management) 제품 신뢰성에 영향을 미치는 중요한 인자는 온도이다. 그러므로 제품의 열 설계는 계획되고 평가되어야 한다. 이 주제의 완전한 토의 는 이 문서의 범의를 넘어선다. 하지만 통상 열 설계 접근법에 대한 제한사항을 언급하는 것은 중요하다. 표 8은 기초적인 열 설계 이슈를 요약한다. 표 9는 전자 장치에 대한 가장 일반적인 냉각 기술과 제한을 요약한다. 표 8 열 설계 사안

표 9 냉각 기술 제한

참고 문헌:

1. MIL-HDBK-251, "Reliability/Design Thermal Applications," 1978.

2. "RAC Thermal Management Guidebook," Reliability Analysis Center, 1995.

3. Steinberg, D.S., "Cooling Techniques for Electronic Equipment," John Wiley and Sons, New York, NY, 1980.

3.2 상호 접속 기술(Interconnection Techniques)

상호접속의 신뢰성은 모든 전자 장비 제조업자들에게 극도의 고려 사항이다. 모든 제품은 몇몇 내부적 그리고 외부적인 접속을 요구 한다. 고장은 부정적인 운용 조건하에서 부식, 기계적인 부하, 진동, 온도 변화 그리고 휴먼 애러 때문에 빈번하게 일어난다. 외부, 와이어, 마운트 표면, 내부 그리고 본딩 컨넥터의 예가 표시된 신뢰성의 관련된 측정과 함께 나타난다.

3.2.1 외부 컨넥터(External Connectors)

그림 4은 세 가지 형태의 외부 컨넥터에 장착하는 예를 보여 준다. 칼날과 포크, 브러시 그리고 박스와 포스트가 있다. 장착물의 그림은 rack(받침대), panel(판), 원형 또는 동축 컨넥테의 실제적인 접속 부품들이다.

그림 4 외부 컨넥터 삽입 예

3.2.2 전선 컨넥터(Wire Connections)

전선을 기둥 또는 핀에 연결하는 것은 손 납땜, crimping/clipping 또는 전선 wrapping으로 할 수 있으며 그림 5에 나타나 있다.

그림 5 전선 연결의 예

3.2.3 표면 실장 연결(Surface Mount Connections)

SMT(표면실장기술을 뜻하는 것으로 전자기기 조립을 자동으로 실행 하는 장치를 총칭한다. 인쇄회로기판(PCB) 위에 반도체나 다이오드, 칩 등을 다수의 장비로 실장하고 이를 경화시키는 기능을 수행하는 기술이다.) 부품은 능동 또는 수동소자 및 다른 리드 설계를 가질 수 있고, 그림 6에 나타나 있다.

그림 6 표면 실장 연결의 예

3.2.4 내부 연결(Internal Connections)

내부적인 접속은 회로기판과 부품 사이에 solder bumps연결, 표면과 표면 사이에 fuzz button 연결, 연결 기판에 Augat Pad Array를 연결 하는 것과 같은 모듈을 연결하는 것이다. 이러한 기술은 그림 7에 나타나 있다. Augat Pad Array 개념은 플런저를 활용하고 접촉 매커니즘은 두 표면 사이가 접촉하여 압축됐을 때 액정고분자 절연 재로 감싸지게 된다.

그림 7 내부 연결의 예

3.2.5 본딩 연결(Bonding Connection)

내부적으로 많은 부품들이 입출력 신호, 전원 또는 자료 라인에 대해 접착이 요구된다. 전형적인 접착 기술은 그림 8에 나타나 있다.

그림 8 본딩 연결의 예

3.2.6 본딩 연결에 대한 설계 Guidelines

가. 제조 결함을 최소화 하기 위해 수동 부품에 대한 가장 큰 허용 기준 크기를 사용한다.

나. 무연과 납이 첨가된 부품을 비교하여 사용을 결정할 때 능동 소자의 적용은 주의 깊게 고려해야 한다.

다. 열 팽창 계수는 무연 납땜 이음에 응력 균열이 발생할 가능성과 매우 근접하게 맞춰야 한다.

라. 휘거나 비틀리는 문제를 피하기 위해 인쇄회로기판(PCB) 크기를 최소화 한다.

마. 제조 연결에 공간을 제공하기 위해 회로 기판 끝부분에 적당한 간격을 제공한다.

바 자동 조제의 쉬운 프로그래밍 또는 장비 배치를 위해 격자 위에 부품들을 위치시킨다.

사. 육안 검사, 재 작업, 조립체의 기술적인 변경을 위해 부품들간 적절한 공간을 허용해야 한다.

참고 문헌:

1. RL-TR-93-6, "Reliability Analysis of Surface Mounted Technology," Rome Laboratory, 1993.

2. RL-TR-92-95 and 96, "Signal Processing System Packaging," Rome Laboratory, 1992.

3. Evans, J.W., "An Overview of Thermally Induced Low Cycle Fatigue in SMT Joints," Surface Mount Technology, February 1989.

4. DeVore, J.A., "The Make-up of a Surface-Mount Solder Joint," Circuit Manufacturing, June 1990.

5. Chakrabarti, K., G. Bivens, and C. Myers, "Electroplastic Creep Analysis of SMT Solder Joints," 1992 Government Microcircuit Applications Conference (GOMAC), 1992.

6. Pai, D.K. and T.A. Krinke, "A Solution to Solder Joint Failure in Leadless Ceramic Chips Carriers," Surface Mount Technology, September 1989.

7. SMT Forum, "Military Surface Mount Applications," Surface Mount Technology, May 1990.

3.3 조립체 수준의 검사 범위(Testability Criteria_Assembly Level)

다음은 조립체 수준에서 좋은 검사 계획 설계를 수행하기 위한 설계 지침을 제공한다. 그림 9은 다양한 카드 수준 검사 접근법을 정의한다.

Module

• Maximize:

- Number of nodes accessible for probes and connections

- Use of standard connector types

- Use of built-in test (BIT) controllable by the automatic test equipment (ATE)

- Hardware partitioning into functionally independent circuits

• Minimize:

- Feedback loops external to the module

- Use of sequential devices

• Provide means to:

- Initialize sequential devices (e.g., counters, shift registers, control flip-flops)

- Control oscillators during test

- Break global feedback loops during test

- Independently test redundant elements

• Utilize:

- Self checking BIT and report all BIT failures

- Coding schemes (i.e., Hamming codes) to test for transmission/storage errors

- Standard pin locations for power, ground, and clock signals

- Vendor generated test vectors for custom devices

• Avoid:

- Use of wired-OR or wired-AND circuitry

- BIT ambiguity groups greater than 5 devices

- Non-isolated BIT circuitry whose failure could disrupt operations

Memory

• Maximize:

- Control lines that are accessible to a connector

- Use of checksum value stored in read only memory (ROM)

• Provide access to:

- Address and control lines at a connector

- Strobe lines in dynamic random access memory (RAM)

- Address generators at connector pins

- Security bit for "secure" ROMs

• Programmable logic devices (PLDs):

- Provide means to disable, while testing, all PLDs driving ROMs

- Lay out all PLDs to minimize all untes표 bridging faults

- Utilize automatic test pattern generators (ATPGs) for PLD test

generation

- Provide means to disable oscillators in PLDs during test

- Make PLD power up state information available

• Avoid:

- Use of programmable read only memory (PROM) requiring 2 voltages

- Memory/PLD device initializations greater than 5 vectors

High Frequency

• Maximize:

- Number of frequency stages with test points

- Use of test points using standard impedances

- Use of standard connectors

• Minimize:

- Manual user interactions

- Length of test point leads and transmission lines

• Utilize:

- Test points designed not to disturb functional signals

- Ground pads with each GHz signal pad

- Signals < 18 GHz and -70 dBm to 60 dBm

High Power

• Utilize:

- Independently controllable and observable parallel power supplies

- Standard test connectors

• Provide access to:

- Power supply internal access nodes

- High voltage transformer taps

- Power supply controls through connector pins

- Test points at amplifier stages

• Safety:

- Ground the surface of the power supply

- Bring only nonhazardous signals out to test points

- Storage devices > 30 volts should discharge within 2 seconds of power down

그림 9 모듈 검사 원천

참고 문헌:

1. RL-TR-92-12, "Testability Design Rating System," Rome Laboratory, 1992.

2. RADC-TR-90-239, "Testability/Diagnostic Design Encyclopedia," Rome Laboratory, 1990.

4. 장비/시스템 신뢰성 고려사항

4.1 시스템 고장 허용 범위

신뢰성을 증가시키기 위한 두 가지 접근법은 고장 회피와 고장 방지 이다. 고장 회피는 전기, 열 그리고 기계적으로 높은 품질의 부품을 사용하는 것과 같은 보수적인 설계를 적용함으로써 성취할 수 있다. 고장 방지는 하드웨어, 소프트웨어 중 하나의 중복 또는 다양한 형식의 자료 중복을 통해서 성취할 수 있다. 고장 방지 노력은 복잡성, 장비 비용, 무게, 부피 그리고 전원 소비를 증가시킨다. 표 10은 일반적인 중복 기술을 요약한다.

표 10 고장 허용 범위 기술 요약

참고 문헌:

1. Siewiorek, D.P. and R.S. Swarz, "The Theory and Practice of Reliable System Design," Digital Press, 1982.

2. MIL-HDBK-338, "Electronic Reliability Design Handbook," 1984.

3. RADC-TR-87-92, "Large Scale Memory Error Detection and Correction Study," Rome Laboratory, 1987.

4. RADC-TR-88-60, "R/M/T Design for Fault Tolerance," Rome Laboratory, 1988.

4.2 환경 특성(Environmental Characterization)

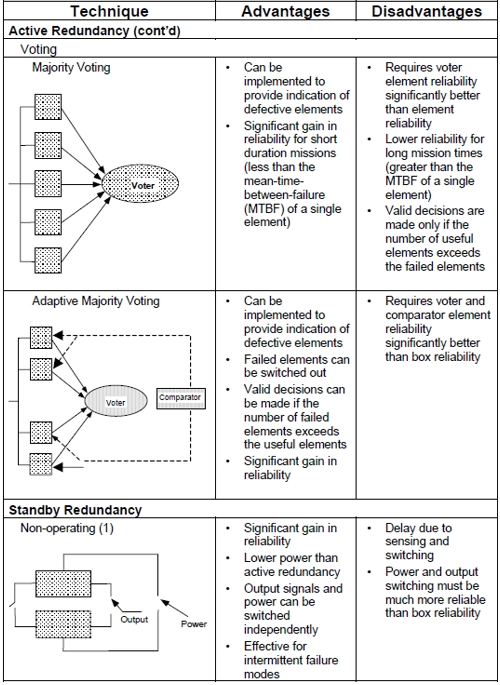

온도, 습도, 진동, 충격, 전원량 그리고 부식과 같은 환경적인 요소 들은 전자 장비의 사용 가능한 수명에 영향을 준다. 장비가 운용되는 환경 조건을 아는 것은 예상된 고장 매커니즘에 관한 안목을 제공한다. 환경적인 부하의 특성을 기술하는 능력은 기존 제품들의 신뢰도를 향상시킬 뿐만 아니라 새로운 제품들의 신뢰성있는 설계에 도움을 준다. 군에서 이는 재시험 통과의 발생 정도를 제어하거나 감소시키는데 도움을 준다. 그리고 높은 부하를 받는 복잡한 전자 시스템에서 35~65% 비율의 고장이 나타나는 것을 설명하는 정비 행위의 중복을 피할 수 없다. 전자장비 축소에 있어서 최근의 진보는 비용 효율적인 환경 부하 측정/기록 장치의 제작과 개발을 가능하게 했다. 이 장치의 사용 예로 상용품은 철도 모니터링, 상업용 비행기 평가, 선적 평가 그리고 교량 상태 모니터링과 같은 응용이 포함된다. 그림 10은 시간 부하 측정 장치(TSMD) 블록 다이어그램을 보여준다.

그림 10 TSMD 블록 다이어그램

4.2.1 수동 환경 기록(Passive Environmental Records)

수동적인 기록장치는 대게 초과하는 온도, 충격 또는 습도의 1회 발생 시간을 측정하는 저 비용 장치이다.

수동 기록장치 포함사항 :

가. 고온 저온 스트립 기록기 : 스트립 기록기는 종이 위에 작은 점으로 침전되는 화학 혼합물의 순서를 제공한다. 각 점은 미리 결정된 온도에서 변하는데 이는 주어진 값을 초과했다는 것을 보여준다.

나. 온도 표시기 : 온도 표시기는 가장 큰 온도를 측정할 수 있다. 표시 재료는 결정된 온도에서 얼거나 또는 색이 변한다.

다. 습도 스트립 기록기 : 다른 습도 수준에서 녹는 크리스탈을 사용해서 스트립 기록기는 습도 수준이 변했을 경우 보여주는 것이 가능하다.

라. 충격 지시기 : 단일 값 지시기는 단일 축을 따라서 설정된 점을 충격 가속이 초과했을 때 알려준다.

참고 문헌:

1. "Market Survey and Product Evaluation Data Recording Equipment," Reliability Analysis Center, PO Box 4700, Rome, NY 13442-4700, (315) 337-0900.

2. McCallum, M., L. Popyack, and J. Collins, "Environmental Measurement and Recording techniques Utilizing a Time Stress Measurement Device (TSMD)," 1990 Proceedings of The Institute of Environmental Science, 1990.

3. Kubler, J. "Environmental Characterization Device Sourcebook," Reliability Analysis Center, 1995.

4. For more information on the active TSMD devices developed by Rome Laboratory, write: Mr. James Collins, Rome Laboratory/ERSR, 525 Brooks Rd. Griffiss AFB, NY 13441-4505.

4.3 치명적인 품목 신뢰성(Critical Item Reliability)

4.3.1 치명적인 품목은 무엇인가

일반적으로, 치명적인 품목은 고장 시 안전, 운용 성공 또는 교환 교체 비용에 있어서 심각하게 영향을 끼치는 제품 또는 구성품이다.

4.3.2 어떻게 치명적인 품목을 식별하는가

치명적인 품목은 고가의 구성품, 새로운 기술 또는 과정, 제한된 수명 품목들, 민감한 신뢰성 품목, 단일 원천 또는 사용자 구성품 그리고 단일 고장 포인트를 포함한다.

4.3.3 무엇이 치명적인 품목을 발생시키는가

가. 필연적인 선진 기술 또는 과정의 사용

나. 좋지 않은 상태에서 구성품의 한계 능력

다. 저급 부품 또는 제품 신뢰성

라. 다른 부품들의 고장을 불러일으키는 고장

마. 고 비용의 주문 설계된 부품들

바. 제한된 또는 치명적인 적용에 대한 단일 판매업자

4.3.4 치명적인 품목 제어(Critical Item Control)

치명적인 품목 관리의 주요 고려사항과 추천된 활동이 표 11의 점검표에 제공된다.

표 11 중요 품목 통제 점검표

주요 고려사항권고된 행동고장 유형 분석은 중요 품목에 대해 고려되었는가?해당 컨트롤을 호출할 수 있도록 고장 모드 식별 절차를 개발설계를 위해 보정 특성이 고려되었는가?안전 여유, 과 부하 시험 또는 고장 허용 범위와 같은 특징들을 고려신뢰성 향상은 고려되었는가?특정한 부하 검사, 조사, 공급업체 품질 절차, 대체 품목, 반복 사용 평가제작 또는 성능에 대해 매우 엄격한 허용 오차가 요구되었는가?대체 공급업체 또는 처리 절차를 채택중요 품목을 제어하기 위해 활용된 검토는 있는가?관리 및 엔지니어링을 위한 정기적인 검토의 표준화기타 고려사항 :

• 안전을 위협하는 고장

• 제한된 수명

• 부품의 단일 공급원

• 고장 나기 쉬운 품목중요 품목 목록과 컨트롤과 검토 절차에 대한 개인적인 책임이 반드시 설립되어야 함

참고 문헌:

1. MIL-HDBK-338, "Electronic Reliability Design Handbook," 1984.

4.4 소프트웨어 신뢰성(Software Reliability)

품질 좋은 소프트웨어 개발은 적소에 잘 정의된 과정 없이 일어나지 않을 것이다. 카네기 멜론 대학의 SEI는 조직 내에 품질 소프트웨어 개발의 제도화 기준을 위해 다섯 가지 수준의 성숙도 평가 모델을 개발하였다. 다섯 가지 수준은 조직의 소프트웨어 공학의 관련된 성숙도를 나타내고, 다섯 가지 수준을 설명하기 위해 단일 용어가 사용 된다.

가. 수준 1 : 초기 - 소프트웨어 과정은 부족하게 제어된다.

나. 수준 2 : 반복적인 - 관리는 소프트웨어 과정의 기본적인 제어를 갖는다.

다. 수준 3 : 정의 - 소프트웨어 과정은 표준 그리고 일관된다.

라. 수준 4 : 관리 - 소프트웨어 과정은 정량적으로 이해되고 제어된다.

마. 수준 5 : 최적화 - 소프트웨어 과정은 지속적인 향상에 초점을 둔다.

성숙도 평가 모델은 18가지 중요 과정 분야가 있고, 조직의 능력을 이해하기 위해 검사되는 300개가 넘는 행위가 있다. 강점과 약점을 이해하는 것은 소트프웨어 공학 과정 그룹의 정체성과 개선을 위한 활동의 우선순위를 매기는 것의 기초를 형성한다.

4.4.1 소프트웨어 개발 모델(Software Development Models)

특정한 소프트웨어 개발 구조를 도울 수 있는 두 가지 모델은 그림 11과 12에 표현되어 있다. 다음 문단에 나타난 자료는 Reed Sorensen이 1995년 1월 CrossTalk edition에 쓴 기사로부터 추론한 것이다. 폭포 모델은 다음 단계로 진행하기 전 각 개발 단계의 완성을 강조한다. 이는 원래 작은 시스템의 개발 또는 기존 소프트웨어의 시스템 업그레이드/개선에 적합하다. Spiral(나선, 소용돌이선) 모델은 증가하는 개발과 시제품화를 수용하기 때문에 큰 소프트웨어 프로젝트에 더 적합하다. Sorensen 기사에 설명된 각 모델의 강점과 약점은 표 12에 주어져 있다.

그림 11 품질 소프트웨어 개발을 위한 폭포 모델

4.4.2 소프트웨어 개발 Guidelines(Software Development Guidelines)

좋은 소프트웨어 개발 업무는 결점 보완 그리고 초기의 실수 밀도를 줄이기 위해 하향식 설계를 중시 한다. 개발의 요구도 단계에서는 훨씬 더 많은 주의를 해야 한다. 부적절하거나 부정확한 요구도는 60 ~ 80%의 소프트웨어 재작업을 유발한다. 재 작업의 비용뿐만 아니라 각 소프트웨어 “패치”는 전체적인 코드의 품질을 떨어뜨리고 미래의 고장을 유발하는 잠재력을 갖는다. 무엇이 소프트웨어 개발에 대한 최선책”이란 용어가 될 수 있는지에 대한 일치된 의견은 없다는 것을 인식해야 한다. 다음의 안내가 제공된다.

가. 요구조건 :

- 고객을 팀의 일원으로 만들어라

- 시장/고객의 요구를 연관된 기술 요구도로 전환하라

- 운용 프로파일을 개발하라

나. 예비 설계(Preliminary Design) :

- 엄격한 항목들의 고장을 정의한다.

- 고객/시장 요구에 부합하기 위한 필수적인 특징과 기술적인 해결책을 식별한다.

- 반드시 하양식 설계를 한다.

- 계획 자료 수집을 한다.

- 설계 검토를 강조한다.

다. 상세 설계(Detail Design) :

- 많은 사용 또는 중요 기능에 대한 공급원에 초점을 맞춘다.

- 소프트웨어 예상 모델을 선정한다.

- 유사한 운용 조건하에서 요구된 신뢰성이 검증되지 않은 상용 소프트웨어의 신뢰성을 검증한다.

- 검사 요구조건과 계획을 설립한다.

라. 부호화(Coding) :

- 특별히 상호 호환과 분할을 고려한 고도로 구성된 코드를 사용한다.

- 코드 검사를 위한 중요한 노력

- 유사한 결함에 대한 코드 대조 검토

마. 모듈 및 시스템 통합(Module and System Integration) :

- 신뢰성 향상 프로그램 수행

- 원인 분석을 위한 인과 관계 분석 팀의 조직

- 결함 밀집도의 예측 및 추적

바. 운용/정비(Operations/Maintenance) :

- 성능 모니터링

- 각각의 식별된 실수의 안전 영향 평가

4.4.3 소프트웨어 개발 접근(Software Development Approaches)

마지막 고려사항으로 소프트웨어 개발을 위한 몇몇 최우선시 되는 기술 또는 철학을 언급한다.

가. 컴퓨터를 이용한 시스템 공학 툴의 사용은 중간에서 큰 소프트 웨어 프로젝트까지내제하는 문제점들을 크게 줄일 수 있다.

나. 소프트웨어 시스템의 워킹 모형을 만드는 과정인 프로토타이핑 은 기술적인 시현 가능성을 증명하고 시스템의 요구조건을 개선하는데 매우 유용하게 사용될수 있다.

다. Cleanroom" 소프트웨어 개발은 가능한 빠르게 버그를 탐지하기 위한 엄격한 과정의 사용을 통해서 소프트웨어에서 오염물질 제거를 유지하는 것을 기획한다.

라. 목표 지향적인 프로그래밍과 분석은 개발의 일상적인 부분을 관리 함으로서 소프트웨어 개발자의 책임감 감소를 시도한다.

4.4.4 소프트웨어 재사용(Software Reuse)

소프트웨어 신뢰성을 향상시키기 위한 다른 가능한 방법은 이미 개발되어 입증된 코드를 사용하는 것이다. 기존에 개발된 코드들의 모듈을 얻기 위해 유용한 많은 재사용 도서관 및 저장소가 있으며, 다음에 요약되어 있다.

참고 문헌: 1. Cobb, R., A. Kouchakdjian, and H. Mills, "The Cleanroom Engineering Software Development Process," Software Technology for Adap표, Reliable Systems (STARS) Program, February 1991. 2. Coad, P., and E. Yourdon, "Object-Oriented Analysis," 1991. 3. RL-TR-93-209, "A Quality Process Approach to Electronic System Reliability," Rome Laboratory, 1993. 4. Sorensen, R. "Comparison of Software Development Methodologies," Software Technology Support Center (STSC) CrossTalk Newsletter, January 1995. (World Wide Web server: http://stsc.hill.af.mil). 5. Carnegie Mellon University Software Engineering Institute World Wide Web Server: http://www.sei.cmu.edu/SEI/HomePage.html. 6. CMU/SEI-93-TR-25, "Key Practices of the Capability Maturity Model, Version 1.1," Software Engineering Institute, 1993. 7. Dymond, K., "A Guide to the CMM," Process Inc., 1995. 8. "Software Engineering Process Group Handbook," Reliability Analysis Center, 1995.

4.5 시스템 수준의 검사 범위(Testability Criteria_System Level)

다음에 제공하는 설계 안내는 시스템 수준에서 좋은 시험성 설계 업무 수행을 위함이다. 그림 13은 시스템 수준의 검사 접근법을 묘사한다.

4.5.1 최상위 수준 설계 고려사항

가. 검사 프로그램 생성에 이용가능한 중요한 신호와 타이밍 다이어그램을 포함한 설계 문서를 만들어라.

나. 표준 검사 부품과 모듈의 사용을 최대화 하라

다. 모든 리던던트 회로는 독립적으로 검사할 수 있도록 하라

라. 다른 컨넥터 형태의 수를 최소화 하라

마. 시스템 수준 번지 그리고 데이터 버스에 직접 접근을 제공하라

바. 시스템과 하위시스템 간의 표준 통신 신호를 사용하라

사. 검사를 위해 중요한 노드에 접근할 수 있도록 하라

아. 검사 장비에 의한 되먹임 루프를 제어 가능할 수 있도록 하라

자. 접근 가능한 표준 시험과 정비 버스를 통합시켜라

차. 전력 부분을 검사할 동안 고 전력 부분이 분리될 수 있도록 용량을 제공하라

카. 표준 검사 기준점의 저항 수준을 50, 75, 130 또는 1 메가 옴 이상으로 하라

타. 고장 분리에 있어서 정비를 돕기 위해 설계하라

4.5.2 시스템 Built-In Test (BIT)

가. 모든 기록된 BIT를 표시하는 타임 스템프를 찍어라

나. 구조 BIT 체계는 각 수준에서 고유의 BIT를 수행하고 이 결과를 하위 수준에 보고하는 것이다.

다. 가능하면 BIT에 자가 검사 특징을 통합하라

라. 주 결함 보고 장치에 있는 결함은 육안으로 명확하다는 것을 확인해라

마. 가능하면 한 개의 회로판 위에 하위시스템 수준 BIT control을 위치하라

바. 검사되는 기능의 10%로 BIT 고장율을 제한하라

사. 모든 BIT 한계값이 쉽게 변경되는 것을 확인하라

아. 모든 내부 연결부 그리고 입/출력에 BIT 검사를 사용하라

자. 모든 시스템의 치명적인 결함은 즉시 사용자에게 확인되게 하라

차. 시스템 컴퓨터로 새로운 시스템 진단 루틴 탑재 능력을 제공

카. 고장 표시 전후에 환경 자료와 BIT를 기록하는 것을 고려하라

그림 13 계층적인 검사

참고 문헌: 1. RL-TR-92-12, "Testability Design Rating System," Rome Laboratory, 1992. 2. RADC-TR-90-239, "Testability/Diagnostic Design Encyclopedia," Rome Laboratory, 1990.

4.6 시스템 전자기 Guidelines

통신, 컴퓨터 사용 그리고 자동화 시스템과 같은 전자 기기의 상업 적인 사용이 증가한 결과 점점더 엄격한 전자기 환경이 만들어 졌다. 이러한 전자장비들은 서로에게 부정적인 영향을 미치지 않고 근접한 거리에서 운용할 수 있는 능력이 있어야 한다. 디자이너의 목표는 이미터를 생산하지 않고 또는 전자기 간섭을 허용할 수 있는 그리고 다른 전자 시스템과 가까이에 있는 동안 호환되고 제대로 작동할 수 있는 전자 시스템을 생산하는 것이다. 전자기 설계의 기초는 그림 14에 나타나 있다. 소스는 커플링 경로를 통해서 응답기로 전송된 전자기 에너지를 생성한다. 수신된 에너지가 의도하지 않은 시스템 응답을 일으키는 원인이 되는 경우에 전자기 효과가 일어난다.

그림 14 전자기 설계의 기초

설계자는 잠재적인 문제점들이 예상되는 설계 단계 초기에 전자기 효과 이슈를 다뤄야 한다. 많은 종류의 전자기 효과를 완화하는 기술을 설계자들이 활용할 수 있다. 만일 문제점들이 설계, 시험 또는 제작 단계 이후까지 다뤄지지 않았다면, 문제를 고치기 위해서는 오직 값비싼 수당을 지불하는 것만 가능하다. 그림 15는 개발 일정, 활용 가능한 설계 기술과 연관된 비용을 보여준다.

참고 문헌:

1. Paul, C.R., "Introduction to Electromagnetic Compatibility," John Wiley & Sons, New York, NY, 1992.

2. Ott, H.W., "Noise Reduction Techniques in Electronic Systems," John Wiley & Sons, New York, NY, 1988.

4.7 기계 시스템(Mechanical Systems)

기계 신뢰성을 이해하기 위한 기초는 부품과 재료 수준에서 기계적인 고장의 과정에 초점을 맞추어야 한다. 기계 고장 과정은 파괴역학, 마찰공학, 재료 과학, 물리, 화학, 금속공학 등과 같은 다양한 기술 적인 학문들을 추적할 수 있는 고장 매커니즘에 의해서 설명된다. 대부분의 기계 고장의 매커니즘은 다음의 기계적인 고장 과정 중 하나에 의해 분류 될 수 있다.

가. 비틀림(Distortion)

나. 피로와 균열(Fatigue and Fracture)

다. 마모(Wear)

라. 부식(Corrosion)

고장 매커니즘 : 고장 발생을 통해 과정을 설명한다. 예) 전식

고장 유형 : 부품, 장비 또는 시스템의 기능 고장의 영향을 설명한다.

고장 원인 : 매커니즘과 포함된 모드에 근거한 결정적인 고장 원인을 설명한다.

환경 효과 : 환경적인 원인, 중요 영향 그리고 수정 활동을 설명한다.

표 14 기계적인 고장의 주요 매커니즘

항공기 시스템에 대한 환경적으로 연관된 분야 고장의 분포는 그림 16에 나타나 있다. 제품의 기계적인 설계에서 다른 환경의 영향과 연관된 수정 활동은 표 15에 설명되어있다.

그림 16 항공 시스템의 환경과 연관된 고장 분포

참고 문헌:

1. Sadlon, R., "Mechanical Applications in Reliability Engineering," Reliability Analysis Center, 1993.

표 15 기계적 설계의 환경적인 영향

4.8 생산품 검토 질문 유형

프로그램과 설계 검토는 비용적으로 재설계를 예방하고 개발 과정을 측정하기 위한 중요한 수단이다. 프로그램의 범위와 크기에 따라서 하나 또는 그 이상의 검토 형태가 표 16에 설명되어 있다. 고객과 설계자 그리고 박식한 개인들의 R&M의 참여는 R&M 성공을 위해 중요한 이슈를 끌어내는 논의를 위해 중요하다. 표 17은 고려되어야 하는 몇몇 더 중요한 이슈의 요약을 나타낸다. 물론, 제기 된 질문은 표에 나타난 것처럼 검토의 타이밍 및 전반적인 개발 프로그램의 범위에 의존한다. 신뢰성 공학자, 프로그램 관리자 그리고 시스템 설계자는 그들이 굳게 만족할만한 확신으로 해결해야 할 신뢰 성 및 정비성 이슈를 follow-up 해야 한다.

표 16 주요 제품 검토

표 17 생산품 검토 점검표

참고 문헌:

1. MIL-HDBK-338, "Electronic Reliability Design Handbook," 1984.

DR Design Review 설계 검토

OEM Original equipment manufacturers 원 장비 제조업자

PMR Product Manufacturing Review 제품 제조공정 검토

PPL Preferred Parts List 우선순위 부품 목록

PRR Product Requirements Review 제품 요구조건 검토

PSAC Parts Selection, Application and Control 부품 선택, 적용 및 통제

RAC Reliability Analysis Center 신뢰성 분석 센터

R&M Reliability and Maintainability 신뢰성과 정비성

SMD Standard Military Drawing 표준 군사 도면

SMT Surface Mount Connections 표면 실장 기술

SEI Software Engineering Institute 소프트웨어 공학 연구소

TSMD Time Stress Measuring Device 시간 부하 측정 장치

![[ILS] 정비성(Maintainability) 설계 Guideline](https://static.wixstatic.com/media/14ef93_25b6e256afba4d77be4b78a28fab62bd~mv2.png/v1/fill/w_593,h_386,al_c,q_85,enc_avif,quality_auto/14ef93_25b6e256afba4d77be4b78a28fab62bd~mv2.png)

![[Training] RCM (Reliability Centered Maintenance)](https://static.wixstatic.com/media/14ef93_7437d65b4827473f87002d8f8321ee4a~mv2.png/v1/fill/w_980,h_743,al_c,q_90,usm_0.66_1.00_0.01,enc_avif,quality_auto/14ef93_7437d65b4827473f87002d8f8321ee4a~mv2.png)

![[Training] QFD (Quality Function Deployment)](https://static.wixstatic.com/media/14ef93_046763be1ac44755bbc21d19de4fea8b~mv2.png/v1/fill/w_743,h_1011,al_c,q_90,enc_avif,quality_auto/14ef93_046763be1ac44755bbc21d19de4fea8b~mv2.png)

댓글